第三章:存储系统

发布于2022-01-06 23:18 阅读(882) 评论(0) 点赞(18) 收藏(1)

第三章:存储系统

Part1:基本概念

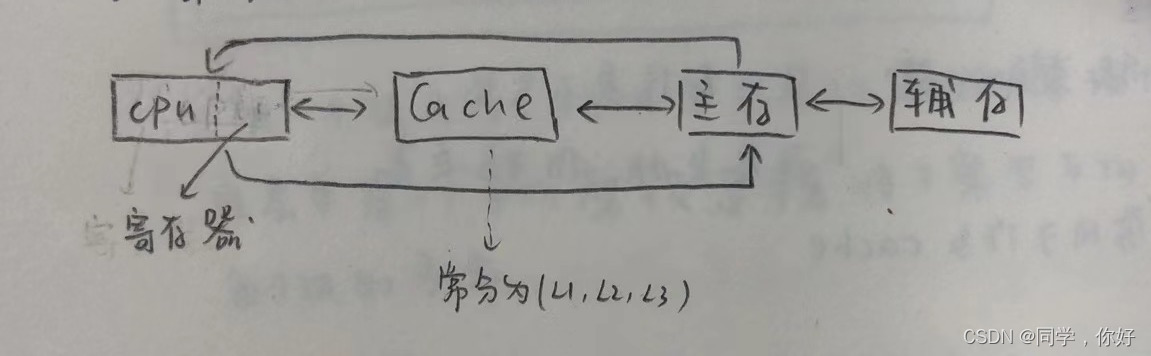

1、存储器的层次结构

2、存储器的分类

-

按照层次分类:详见1的图

-

按照存取方式分类:

-

RAM(Random Memory):任意单元可以随机读取,易失性(断电后数据消失)

- SRAM

- DRAM

-

ROM(Read Only Menory):只读不写(BIOS常放置于ROM中),非易失性(断电后数据不消失)

-

CAM(Conent-addresseable Memory):相联存储器,可以按照内容访问主存(常用于快表中)

-

3、性能指标

- 容量:字数*字长

- 存取

- 存储周期:存取时间+恢复时间

- 存储时间:读出时间+读入时间

Part2:存储器硬件

1、RAM

-

分类

-

DRAM:Dynamic RAM,采用栅极电容(单个MOS管)

- 读出后信息丢失,需要再生

- 一段时间后(2ms)后信息丢失,需要刷新

- 由于其集成度高,常用于主存

-

SRAM:Static RAM,采用双稳态触发器(6个MOS管)

- 读出后信息不丢失

- 速度更快,价格很高,集成度不高

- 常用于作为cache

-

-

DRAM

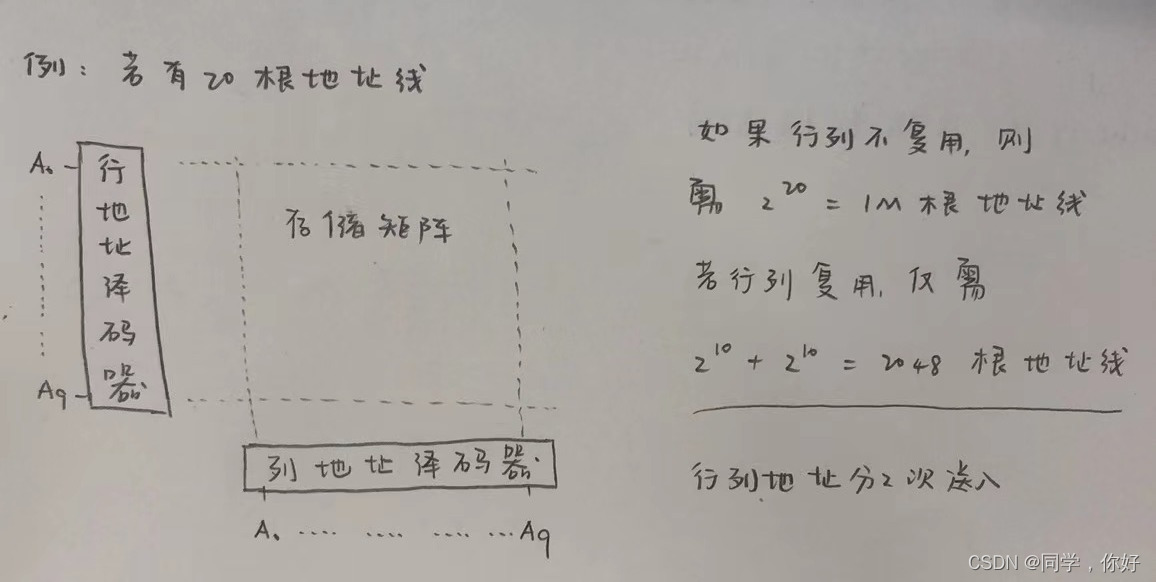

2.1 地址线复用

有DRAM地址容量过大,故其地址线数量太多,实现起来非常的困难,故采用地址线复用的技术

2.2 刷新

- 分散刷新:每次读写完毕均刷新一次

- 集中刷新:2ms内集中一段时间刷新一次,这段时间被称为死区

- 异步刷新:以上两点的综合,即2ms内每行刷新一次即可,当有1024行的只需2/1024=1.95us刷新一次

2.3 发展

现在的DDR3、DDR4采用的技术为SDRAM(Synchronous DRAM)同步DRAM技术

2、ROM

-

Flash

在EEPROM基础上发展而来,可以多次擦写,但由于其需要先擦候写,所以写速度比读速度更慢

-

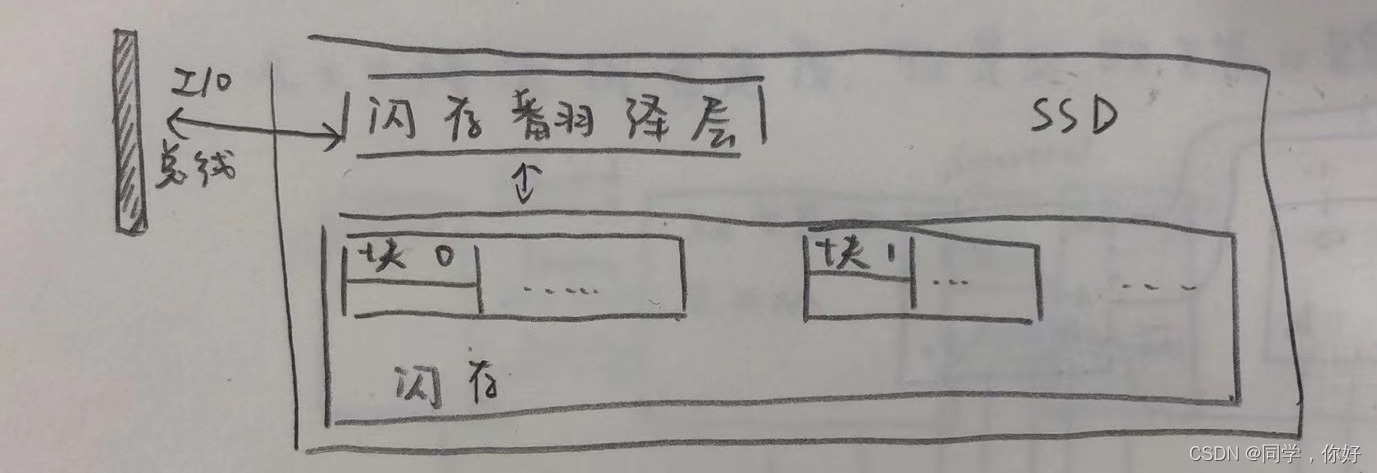

SSD(Solid State Drives)固态硬盘

由控制单元和存储单元(Flash芯片)构成

一般一个块进行10万次重复写之后就会磨损坏而不能使用,在闪存翻译层中有一个“平均磨损逻辑”将擦写平均分布在每个块上来最大化每个块的寿命,实际上这个“平均磨损逻辑”做的非常好,SSD需要很多年才会坏掉

-

BIOS芯片

该芯片存储了自举装入程序,负责装入操作系统

Part3:主存储器

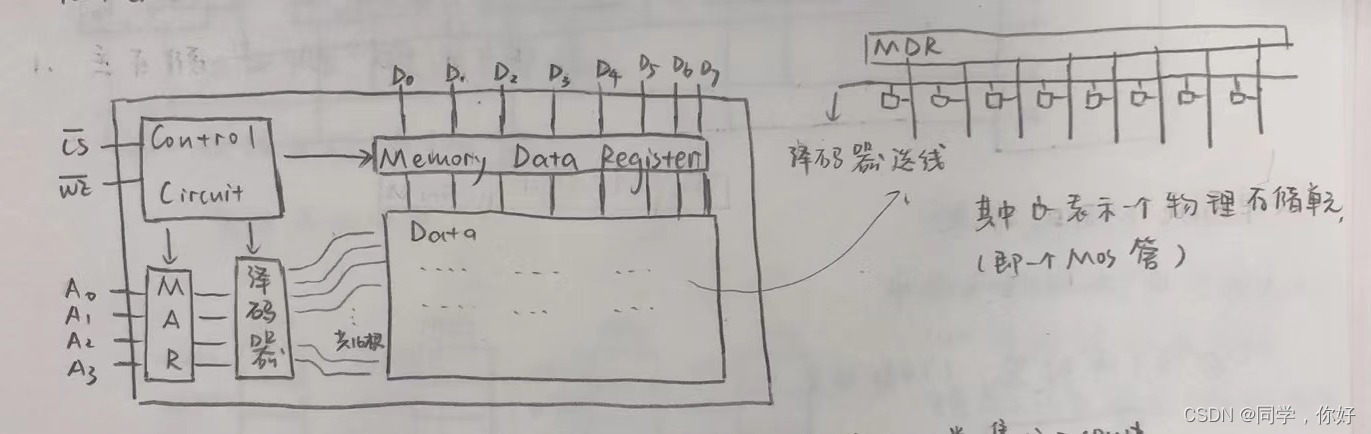

1、主存储器硬件结构

- 译码器:将MAR地址翻译为选择连通那根线

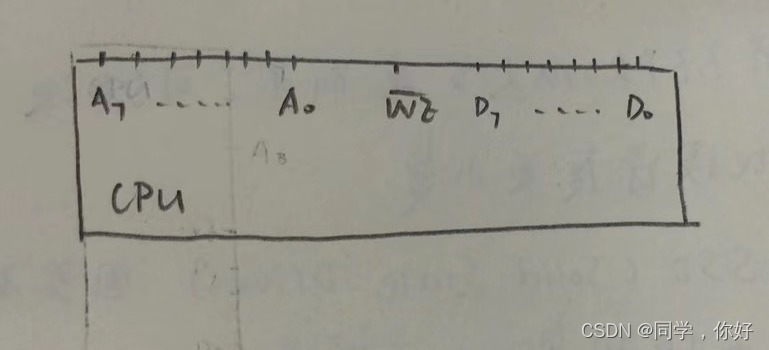

- MAR,MDR:现代计算机中常集成于CPU中

- Control Circuit(控制电路):当MAR,MDR中的输入/输出电信号稳定后在打开读写权限

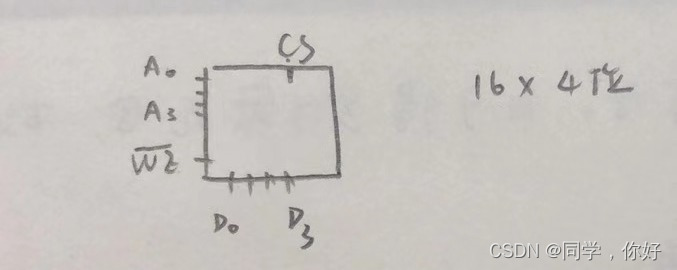

- A0~A3:数据的地址引脚; D0~D7:数据的内容引脚

- CS/CE(Chip Select/Chip Enable):芯片选择开关(图中头上带个帽子表示低电平有效)

- WE(Wirte Enable):读写开关,当然也可以使用2个开关来实现(WE+RE)

2、主存容量扩展

将1中的芯片抽象为

将CPU抽象为

-

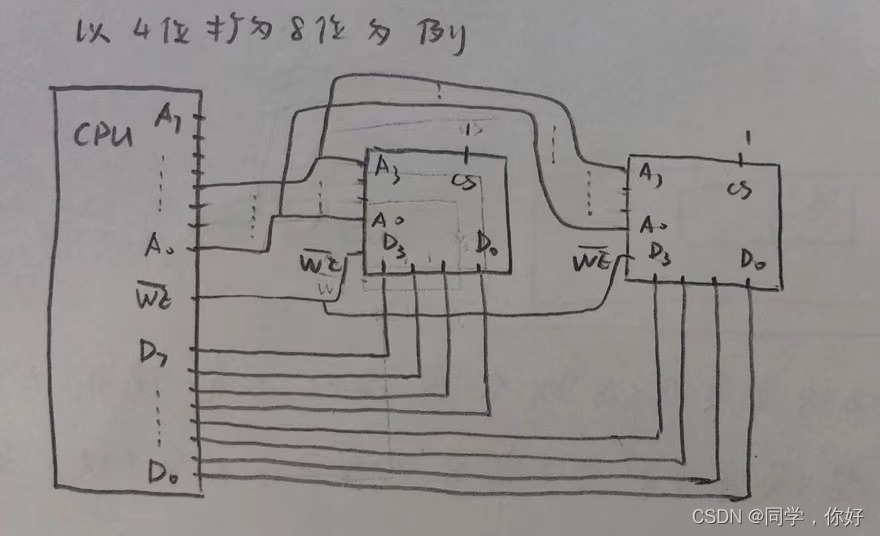

位扩展:将4位扩展至8位

-

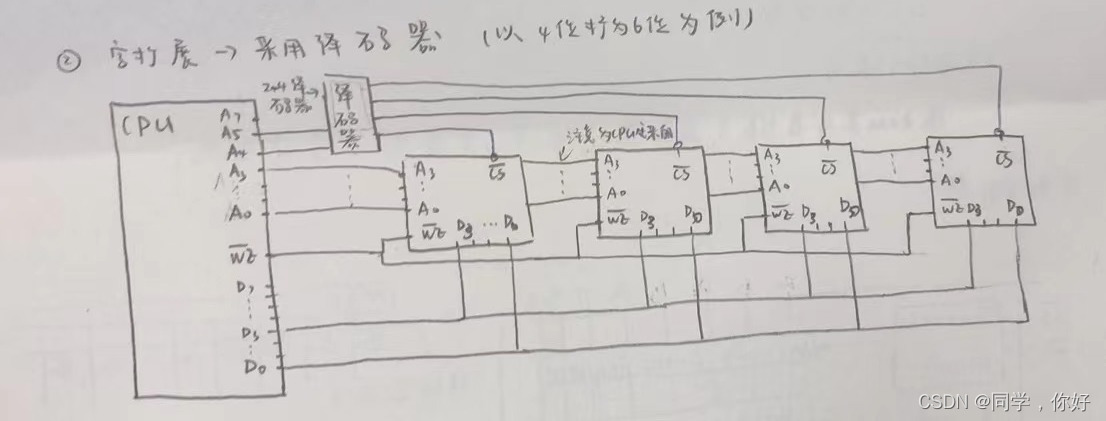

字扩展:采用译码器,将4位扩展至6位

-

字位通知扩展:1和2的结合

-

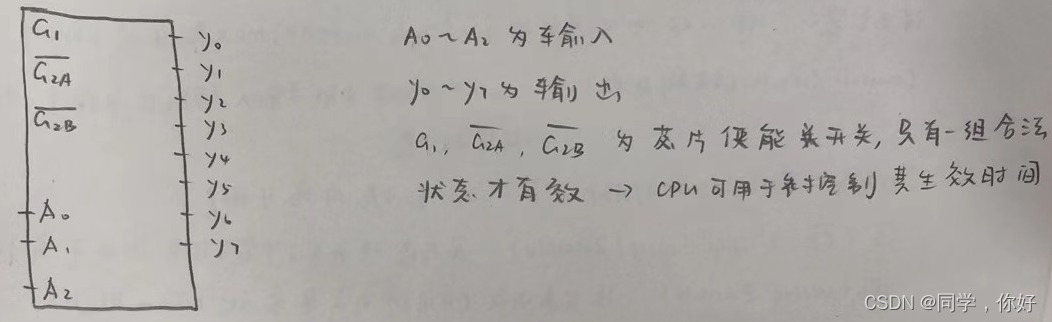

关于译码器:74ls138

3、提升CPU访问主存速度

采用并行技术

- 空间并行:双端口RAM

- 时间并行:多模块存储器

- 单体多字

- 多体并行(低位交叉)

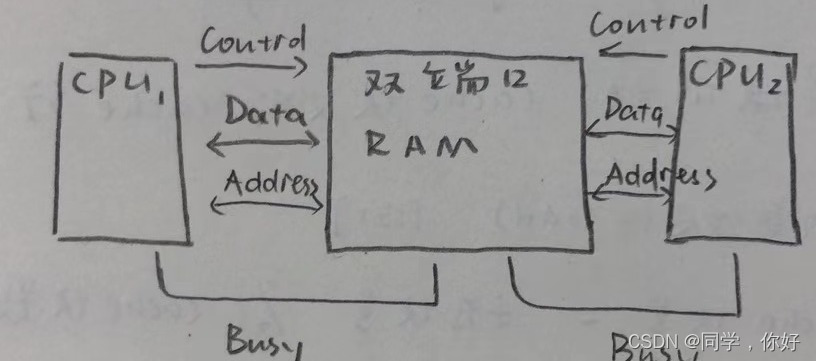

3.1 双端口RAM

现代CPU大多是多核CPU,如果对这些核心采用依次访存的方式,则会大大降低其访存速度。故提出双端口RAM,即让多个核心同时访存。下面以2个核心为例,为了防止出现同时写和一方读一方写的情况,增加了一个busy线,当一方写时,另一方不能操作。

3.2多模块存储器

-

单体多字

虽然只要一个存储体,但是每个单元存储了多个字,每次读写均可读出多个字,提升了带宽

-

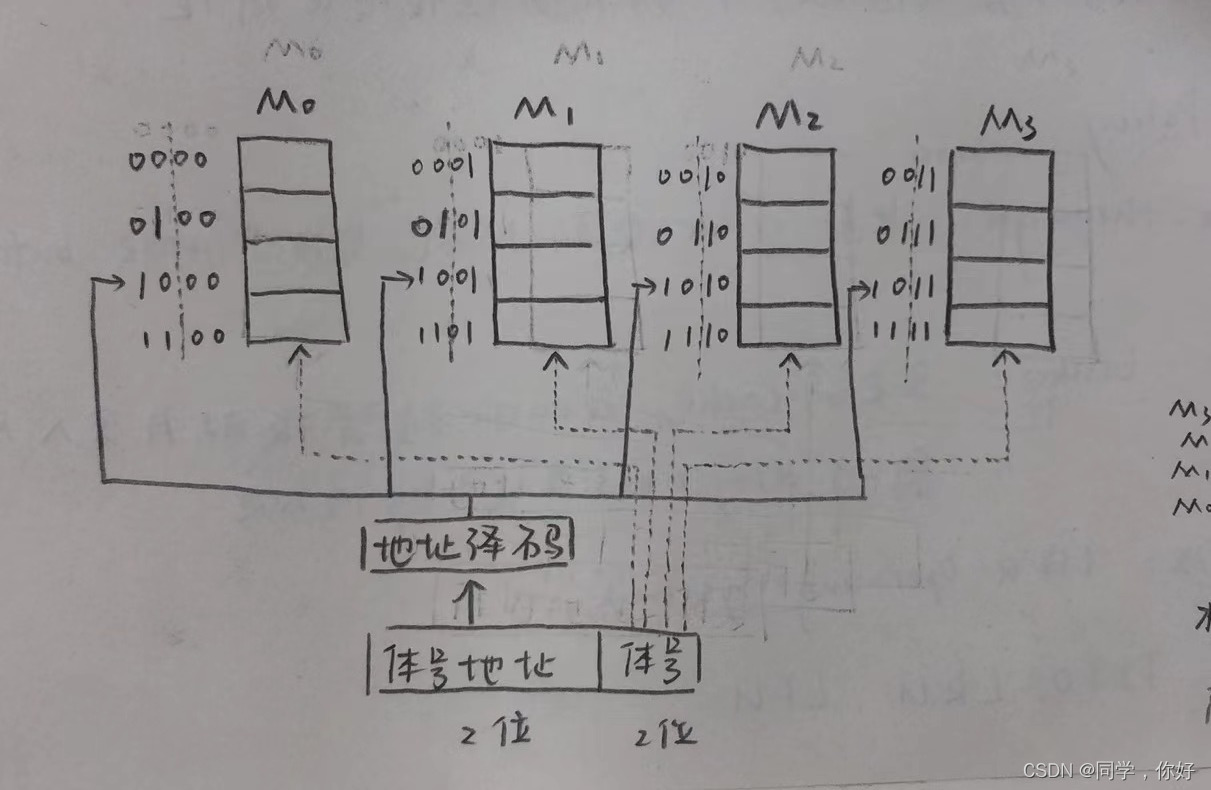

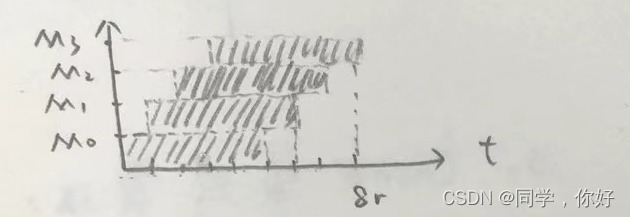

多体并行

由于内存采用了DRAM技术,每次读出为破坏性读出,需要时间再生。故

T 读 = T 读 数 据 + T 再 生 数 据 T_{读}=T_{读数据}+T_{再生数据} T读=T读数据+T再生数据

一般来说T读数据<T再生数据假设T再生数据=4*T读数据

则我们设置4条内存条

CPU从0000一直读取到0011之后,存储器M0刚好恢复,又可以开始读取,从而消除了时延,本质上是用了程序的局部性原理,来加速,运用这个原理来加速,在后面的内容和操作系统中我们将会多次运用到

Part4:高速缓冲存储器cache

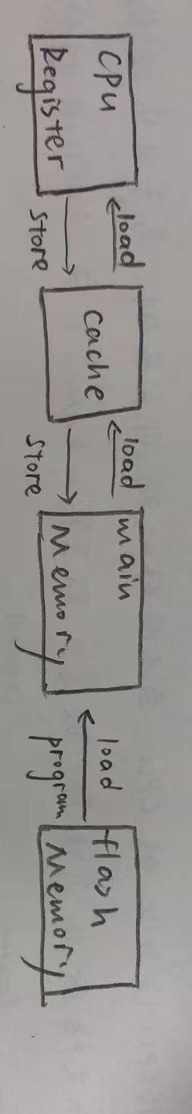

由于程序的局部性原理,我们需要使用的那片内存空间其实不大,但是CPU寄存器和内存之间的速度差异实在是太大了,故我们引入一个缓冲器来缓和这种速度矛盾,这个缓冲器称之为cache

Cache和Main Memory会划分成大小相等的块,cache块又称为cache行

1、MM–>Cache

从主存中将数据加载到cache中,是以块为单位进行的1

-

直接映射

cache块号=主存块号%cache块数

其地址结构为:

标记(Tag) cache行号 块内地址 -

全相联映射

主存中的块可以装入cache中的任意地址

其地址结构为

标记(Tag) 块内地址 -

组相联映射

1和2的折中方案,将cache划分为大小相等的组,组内全相联,组间直接映射,一个组中有几个cache块成为几路组相联。

组号=主存块号%组数

其地址结构为

标记(Tag) 组号 块内地址

2、Cache更新策略

- 直写法(write-through):更新cache之后马上更新主存,常用一个write buffer来写入主存

- 回写法(write-back):只更新cache中的内容,当cache被替换时才考虑是否写入主存,如果该cache被修改过则写入主存,因此需要一个脏位来记录其是否被修改过

3、Cache置换算法(详见操作系统)

FIFO、LRU、LFU

Part end:参考文献和一些说明

一个完整的cache内容,分为数据部分和信息部分,比如一个cache行大小为64B,并不都是用于存储数据的,还需要存储信息部分。而信息部分至少包含1位有效位,Tag字段(虚拟地址前几位)有效位表示该部分内容是否在cache中。 ↩︎

原文链接:https://blog.csdn.net/qq_45712772/article/details/122324317

所属网站分类: 技术文章 > 博客

作者:代码搬运工

链接:http://www.qianduanheidong.com/blog/article/284427/40f8e968376212f6b2ae/

来源:前端黑洞网

任何形式的转载都请注明出处,如有侵权 一经发现 必将追究其法律责任

昵称:

评论内容:(最多支持255个字符)

---无人问津也好,技不如人也罢,你都要试着安静下来,去做自己该做的事,而不是让内心的烦躁、焦虑,坏掉你本来就不多的热情和定力